ORACLE

# **Dynamic paravirt lock-ops**

For a dynamic world

Ankur Arora ankur.a.arora@oracle.com

1 / 18 | Copyright © 2020 Oracle and/or its affiliates | Oracle Public | October 16, 2020

### Contents

- Motivation

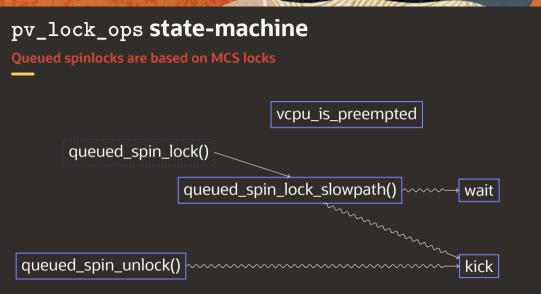

- pv\_lock\_ops state-machine

- What does switching pv\_lock\_ops involve?

- Patching mechanism: INT3

- V1 patchset

- V2 design

## **Guests should be more dynamic**

KVM\_HINTS\_REALTIME=1 => native pv\_lock\_ops<sup>1</sup> KVM\_HINTS\_REALTIME=0 => paravirt pv\_lock\_ops<sup>2</sup>

A guest that starts with KVM\_HINTS\_REALTIME, and then becomes oversubscribed: typically ends in softlockups.

The recommended fix is that a host should only advertise KVM\_HINTS\_REALTIME if it can guarantee it for the lifetime of the guest.

<sup>1</sup>Hypervisor specific ops are paravirt\_nop()

<sup>2</sup>KVM's hypervisor specific ops are kvm\_wait(), kvm\_vcpu\_kick()

copyright © 2020 Grade and/or its affiliates | Oracle Public | October 15, 2020

# Why don't we just use paravirt locks all the time?

#### Unlock fastpath

- movb \$0, (%rdi)

- lock cmpxchg %dl,(%rdi)

Paravirt queued\_spin\_lock\_slowpath are pessimistic by default

What does switching pv\_lock\_ops involve? Switch all call-sites, kernel and modules, for all 5 interfaces atomically<sup>3</sup>

Transform back and forth between instruction sequences like this one for queued\_spin\_unlock

\_\_native\_queued\_spin\_unlock: 0: c6 07 00 movb \$0x0,(%rdi) 3: 0f 1f 40 00 nopl 0x0(%rax) \_\_pv\_queued\_spin\_unlock: 0: e8 31 e6 ff ff callq 0xffffffffffffff636 5: 66 90 xchg %ax,%ax

<sup>3</sup>queued\_spin\_unlock() is almost always inlined <sup>16</sup> | Copyright © 2020 Grade and/or its affiliates | Oracle Public | October 16, 2020

# What does switching pv\_lock\_ops involve? (contd.)

- Other ops might go from CALL+NOP2 (pv\_lock\_ops.wait = kvm\_wait()) to NOP7 (pv\_lock\_ops.wait = paravirt\_nop()) or back

- Spinlocks cannot sleep:

- So no references to stale pv\_lock\_ops opcodes on the stack

### **Active users**

... while we are patching

#### Contexts

- Tasks

- Softirqs

- Interrupt handlers

- IPIs in particular get used from text\_poke\_bp() while patching

- NMI handlers

- All of the above, but nested.

Remember, I said spinlocks (thus pv\_lock\_ops) cannot sleep.

• They can get context switched out in the hypervisor

## Mechanism: INT3

Patching while potentially executing code that you are patching. Enter INT3.

- Standard Linux mechanism for modifying cross-modifying code

- Single byte breakpoint instruction: opcode OxCC

- Used as a barrier at entry

- Assuming a single entry point to instruction sequence

- If this barrier is hit, the control flow shifts to an INT3 handler

- Which emulates the original target or the new

# V1: approach

#### Use stop\_machine()

- lock-step state-machine on all the VCPUs

- Inner loop on CPU-patcher and all the secondary CPUs waiting to synchronize at each step.

- interrupts are disabled

- no IPIs needed for sync\_core()

- no pv\_lock\_ops on the stack: all VCPUs are executing in stop\_machine()

- NMIs are the only risk

- the INT3 handler also implements a subset of this state-machine, so we can make forward progress if the primary or a secondary CPU hit an NMI<sup>4</sup>

<sup>4</sup>Multiple simultaneous NMIs complicate the handling somewhat.

0 / 18 | Copyright © 2020 Oracle and/or its affiliates | Oracle Public | October 16, 2020

### V1: state-machine

CPU-x CPU-patcher /\* CALL, NOP2: e8 31 e6 ff ff 66 90 \*/ write-INT3 /\* INT3, ... : cc 31 e6 ff ff 66 90 \*/ sync() smp-cond-load-acquire(state == INT3-written) sync() /\* INT3. ... : cc 07 00 0f 1f 40 00 \*/ write-rest sync() smp-cond-load-acquire(state == rest-written) sync() /\* MOV. NOP4 : c6 07 00 0f 1f 40 00 \*/ write-first-byte sync() smp-cond-load-acquire(state == first-written) sync()

### V1: last words

lt worked, but ... stop\_machine()

A review comment said: "bonghits crazy code."

Which was pretty understated, in hindsight.

# V2: design

Where I magically discover a less crazy way to do this...

#### Step1: prefix INT3

- Use INT3 (0xCC) as a site-local barrier; everywhere

- Allows us to enforce atomicity while patching multiple sites

- Step2: global "barrier"

- Divides the guest state into pre and post stages: old and new pv\_lock\_ops

- Meanwhile the INT3 handler emulates old or new pv\_lock\_ops

Step3: finish patching

• Use the protection offered by INT3 (0xCC) to finish writing the new opcodes

## V2 design: global barrier

Sure, but how...

The transition point in old to new  $pv_locks_ops$  requires a point where no ops are executing.

A CPU after crossing the barrier:

- Counts all spinlocks<sup>5</sup> under execution

- Counting happens in the INT3 handler

<sup>5</sup>Figuratively, not literally. We have no way of counting locks, we can, however, count entry in queued\_spin\_slowpath() and exit in queued\_spin\_unlock()

# V2 design: global barrier

```

atomic_t barrier_cpus, active_lock_ops;

DEFINE_PER_CPU(int, paravirt_switch_barrier);

void patch_barrier(void) {

this_cpu_write(paravirt_switch_barrier, 1);

atomic_inc(&barrier_cpus);

/* Count active_lock_ops if this_cpu_read(paravirt_switch_barrier). */

}

```

Property that needs to hold:

atomic\_read(&barrier\_cpus) == num\_online\_cpus

&& atomic\_read(&active\_lock\_ops) == 0;

Once this holds, INT3 handling can start emulating the new pv\_lock\_ops and move to Step 3.

# V2 design: more on counting

What are we counting?

- not counting the fastpath: queued\_spin\_lock() ... queued\_spin\_unlock()

- count the slowpath: queued\_spin\_lock\_slowpath() ... queued\_spin\_unlock()

Use a bitmap to be able to tell the two calls to queued\_spin\_unlock() apart.

Note that spinlocks can be arbitrarily nested, in each of the four contexts (thread, softirq, interrupt, NMI)

### Show me the code

#### V2:

• https://github.com/terminus/linux/tree/alternatives-v2

V1:

- https://github.com/terminus/linux/tree/alternatives-rfc-upstream-v1

- https://lore.kernel.org/lkml/20200408050323.4237-1ankur.a.arora@oracle.com/

Or send them to ankur.a.arora@oracle.com.

0

18 / 18 | Copyright © 2020 Oracle and/or its affiliates | Oracle Public | October 16, 2020