KVM Forum November 1, 2019

### QEMU<sup>™</sup> for Qualcomm<sup>®</sup> Hexagon<sup>™</sup> Automatic Translation of VLIW DSP Instructions to Tiny Code

Niccolò Izzo *rev.ng* L Taylor Simpson *Qualcomm Innovation Center, Inc.*

Qualcomm Hexagon is a product of Qualcomm, Technologies, Inc. and/or its subsidiaries. QEMU is a trademark of Fabrice Bellard.

## About rev.ng

A Milan-based startup founded 2 years ago by two researchers from Politecnico di Milano

Key business areas:

- Static and dynamic binary translation

- Compilation and program analysis techniques

- Architecture-independent decompiler (binary to C)

Niccolò Izzo MSc Computer Science and Engineering (cum laude) - 2017 Pursuing PhD at Politecnico di Milano

Master Thesis on Rowhammer Maintainer of <u>LineageOS for MicroG</u> Twitter: <u>@n1zzo</u> Email: <u>nizzo@rev.ng</u> Callsign: IU2KIN

### About Qualcomm

Qualcomm invents breakthrough technologies that transform how the world connects, computes, and communicates. When we connected the phone to the Internet, the mobile revolution was born. Today, our inventions are the foundation for life-changing products, experiences, and industries.

L Taylor Simpson Sr. Director, Engineering LLVM compiler and tools team Qualcomm Innovation Center, Inc. PhD Computer Science – Rice University tsimpson@quicinc.com

# **QEMU Hexagon**

Overview

- Introduction to Hexagon

- Introduction to QEMU

Tiny Code Generator (TCG)

- Challenges

- Automated TCG generation

- Qualcomm approach

- rev.ng approach

- Status and next steps

- Conclusion

# Introduction to Hexagon

### Introduction to Hexagon

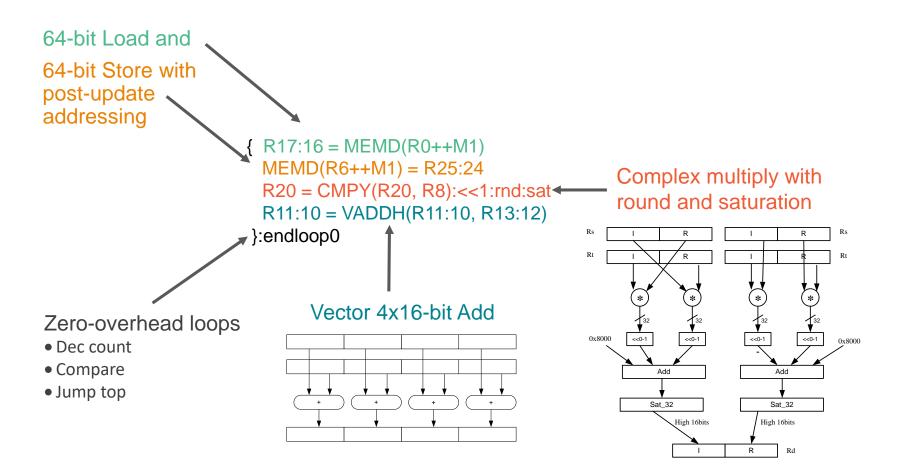

#### Very Long Instruction Word Digital Signal Processor (VLIW DSP)

Example from inner loop of FFT: Executing 29 "simple RISC ops" in 1 cycle

# Introduction to QEMU

# Introduction to QEMU

#### • <u>qemu.org</u>

- Generic and open source machine emulator and virtualizer

- Code translation drives fast off-target simulation

- Operating modes

- $\circ$  User mode

- System mode

- Virtualization

- Trace-based translator

- Unit of translation is a translation block

- Target instructions are translated to TCG ops

- $\circ$  TCG ops are then transformed into host instructions

- Translate once, execute many times

# Introduction to QEMU

Tiny Code Generator (TCG)

TCG operators

tcg\_gen\_<op>[i]\_<size>

<op> is the operation (e.g., add)

[i] indicates immediate instead of register (e.g., addi)

<size> is the size of TCG registers (usually use tl shorthand)

Example: tcg\_gen\_add\_tl

• From x86 assembly instruction to tiny code instructions

0x1000: call 0 x2000 0x1005:

sub\_i32 tmp0 ,esp , \$0x4

qemu\_st\_i32 \$0x1005 ,tmp0 ,leul ,0

mov\_i32 esp , tmp0

movi\_i32 eip , \$0x2000

## Introduction to QEMU

- Goal: Create qemu-hexagon

- Translate binary Hexagon packets to TCG

```

{ R17:16 = MEMD(R0++M1)

MEMD(R6++M1) = R25:24

R20 = CMPY(R20, R8):<<1:rnd:sat

R11:10 = VADDH(R11:10, R13:12)

}:endloop0

```

# Challenges

## Challenges

Packet semantics

Behavior is NOT the same as executing instructions sequentially

{ r0 = r1; r1 = r0 } // Swap r0 and r1

$\circ$  Dual jumps  $\rightarrow$  Only one is executed

{ if (p0) jump:nt <foo>; jump <bar> }

$\circ$  Dual stores  $\rightarrow$  Stores are serialized

{ memw(r3+#0) = r5; memb(r3+#0) = r4 }

• .new

{ if (!p0.new) r0=#13; p0=cmp.eq(r0,#4) }

$\circ$  Multiple predicate definitions  $\rightarrow$  and them together

{ p0=cmp.eq(r0,r1); p0=cmp.eq(r2,r3) }

$\circ$  Precise interrupts and exceptions  $\rightarrow$  All instructions commit or none commit

```

Over 2,000 user mode instructions!

```

## Challenges

Implementation

QEMU executes tiny code instructions in sequential order To preserve semantics, we have to

- Reorder instructions to solve dependencies

- Use temporary register set for .new accesses

- Commit at the end of packet to actual registers

- Commit only if no exception occur

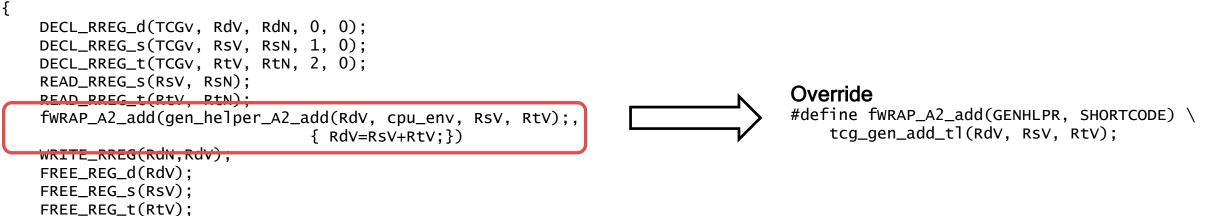

Automated Instruction Generation QTI approach

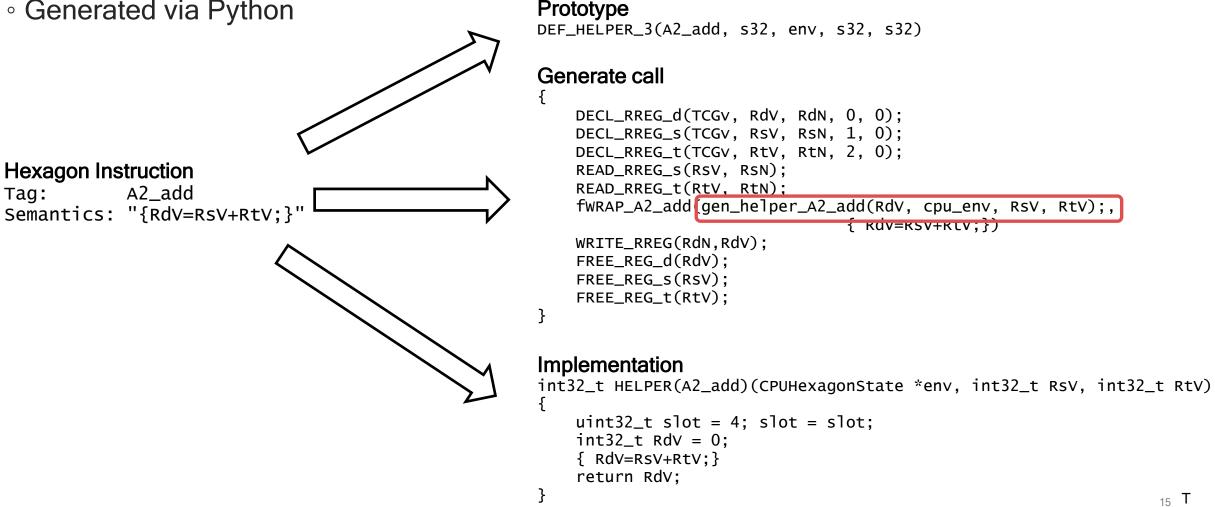

## QEMU "helper"

- QEMU uses "helpers" to call function from TCG

- Each helper has 3 parts

- Generated via Python

# QEMU "helper"

- Advantage

- Very quickly implement all instructions

- Same semantics as hexagon-sim

- Disadvantages

- Function call overhead

- Barrier to TCG optimization

#### Generate

}

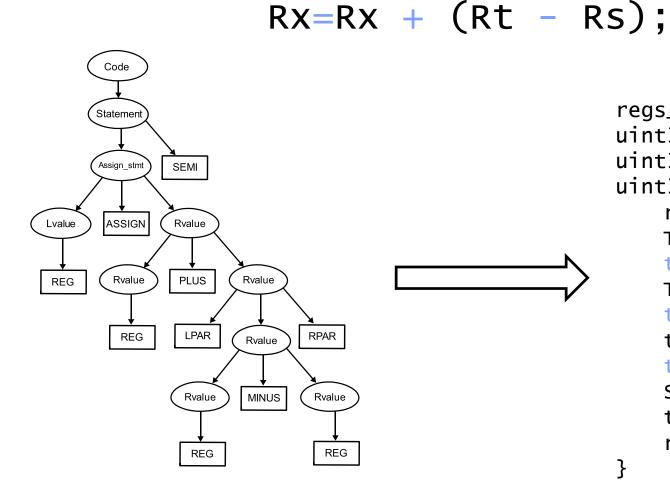

Automated Instruction Generation rev.ng approach

Hexagon instructions are described in the docs with C-like snippets, e.g.:

Assembly syntax

Rx=Rx + (Rt - Rs);

Pseudo-code

Can we translate these snippets into QEMU TCG generation code?

Hexagon instructions are described in the docs with C-like snippets, e.g.:

Assembly syntax

Rx=Rx + (Rt - Rs);

Pseudo-code

Can we translate these snippets into QEMU TCG generation code?

We used flex + bison to achieve exactly that

flex-bison syntax tree

regs\_t function\_536(DisasContext \* dc , uint32\_t x, uint32\_t t. uint32\_t s) { reqs\_t reqs =  $\{0\}$ ;  $TCGv_i32 tmp_0 = tcg_temp_new_i32$  (); tcg\_gen\_sub\_i32(tmp\_0 , GPR[t], GPR[s]);  $TCGv_i32 tmp_1 = tcq_temp_new_i32$  (); tcg\_gen\_add\_i32(tmp\_1 , GPR[x], tmp\_0 ); tcg\_temp\_free\_i32(tmp\_0 ); tcg\_gen\_mov\_tl(GPR\_new[x], tmp\_1); SET\_USED\_REG(regs , x); tcg\_temp\_free\_i32(tmp\_1 ); return regs;

TCG generation function

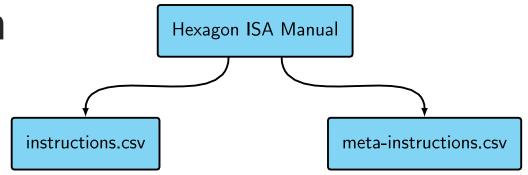

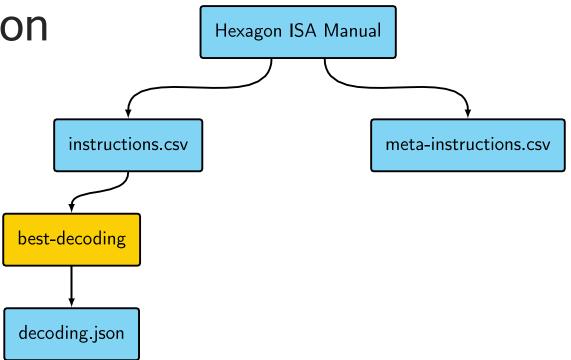

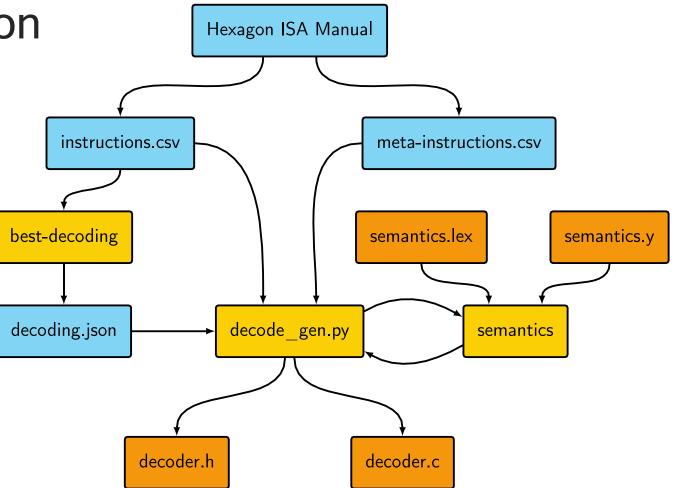

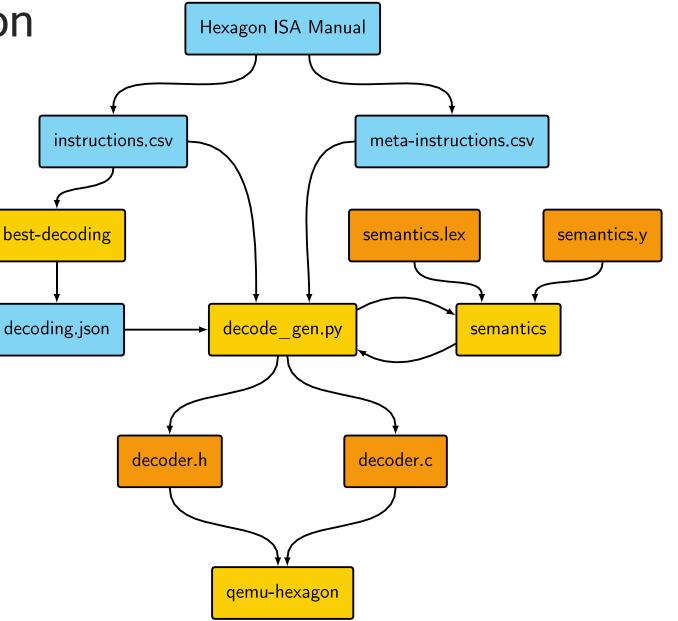

Two *CSV* are extracted from the ISA manual containing the instruction **encodings** and **semantic descriptions**

Two *CSV* are extracted from the ISA manual containing the instruction encodings and semantic descriptions

An optimized decoder tree is generated from the encodings

Two *CSV* are extracted from the ISA manual containing the instruction **encodings** and **semantic descriptions**

An optimized decoder tree is generated from the encodings

The pseudocode snippets are fed into a flex-bison generated parser

Two *CSV* are extracted from the ISA manual containing the instruction **encodings** and **semantic descriptions**

An optimized decoder tree is generated from the encodings

The pseudocode snippets are fed into a flex-bison generated parser

The resulting functions are used to generate a source and header file, which are **compiled into QEMU**

# Status and Limitations

### Status

- Up to 28X faster than hexagon-sim

- Linux user space completed

- Angel/semi-hosting

- Extensively tested

- Code available

- rev.ng implementation

- Qualcomm implementation

https://github.com/revng/qemu-hexagon https://github.com/quic/qemu

## Next Steps

- Short term

- Merge rev.ng and QTI implementations

- Community review

- Merge upstream

- Long term

- Tighter integration with Hexagon LLVM

- System mode

- Debug Hexagon programs with LLVM debugger (LLDB)

# Demo & Conclusion

### Conclusion

- VLIW semantics create interesting challenges

- Large number of instructions requires automated generation

- Code generator can be useful for adding support for new complex architectures

- Hexagon programs execute up to 28X faster on QEMU than current simulator

Qualcom

# Thank you!

Follow us on: f ♥ For more information, visit us at: www.qualcomm.com & www.qualcomm.com/blog

Nothing in these materials is an offer to sell any of the components or devices referenced herein.

©2018-2019 Qualcomm Technologies, Inc. and/or its affiliated companies. All Rights Reserved.

Qualcomm and Hexagon are trademarks of Qualcomm Incorporated, registered in the United States and other countries. Other products and brand names may be trademarks or registered trademarks of their respective owners. References in this presentation to "Qualcomm" may mean Qualcomm Incorporated, Qualcomm Technologies, Inc., and/or other subsidiaries or business units within the Qualcomm corporate structure, as applicable. Qualcomm Incorporated includes Qualcomm's licensing business, QTL, and the vast majority of its patent portfolio. Qualcomm Technologies, Inc., a wholly-owned subsidiary of Qualcomm Incorporated, operates, along with its subsidiaries, substantially all of Qualcomm's engineering, research and development functions, and substantially all of its product and services businesses, including its semiconductor business, QCT.